テクノロジー

ミックスドシグナル技術

デジタル・アナログ混載

モバイルコミュニケーション、ネットワーキング、車載、FA、ロボティクス、医療など、さまざまな分野で利用される電子機器には、高機能化だけでなく小型・低消費電力化も求められます。そうしたなかで重要性を増しているのが、デジタル回路とアナログ回路を混載するミックスドシグナル技術です。

高集積化の進展とともに複雑度を増すミックスドシグナルSoC設計には、ノイズ対策、信号品質、熱対策、PKG設計、PCB設計に対する知識と技術が必要不可欠です。メガチップスは、デジタル・アナログとも豊富な経験に基づく幅広い知見を蓄積しており、それらを駆使したミックスドシグナルソリューションを提供しています。

高速シリアルインターフェース

メガチップスは、PON(Passive Optical Network)向けSerDes、ディスプレイ用Timing Controller向けV-by-One、eDP(embedded DisplayPort)といった高速シリアルインターフェースの分野で15年以上の経験を持ち、現在も研鑽を続けています。その間に蓄積してきたバーストモードCDR(Clock Data Recovery)SerDes技術は、幅広いPONスタンダードに対して柔軟に対応することが可能であり、国内外で幅広く使用されています。また、マルチプロトコル対応の高速SerDesもサポートしており、さまざまな高速シリアルインターフェースに対応可能です。

特徴

- 超高速バースト・データ・ロックCDR

- フレキシブルなレーン構成

- マルチプロトコル対応

対応スタンダード例

- 10G-EPON/XGPON: 1Gbps~10.3125Gbps

- マルチプロトコル(PCI-Express Gen1-4, SATA1-3, JESD204B, etc.)

- V-by-One: 1.62Gbps~4.0Gbps

- eDP: 1.62Gbps~5.4Gbps

AFE(Analog Front End)

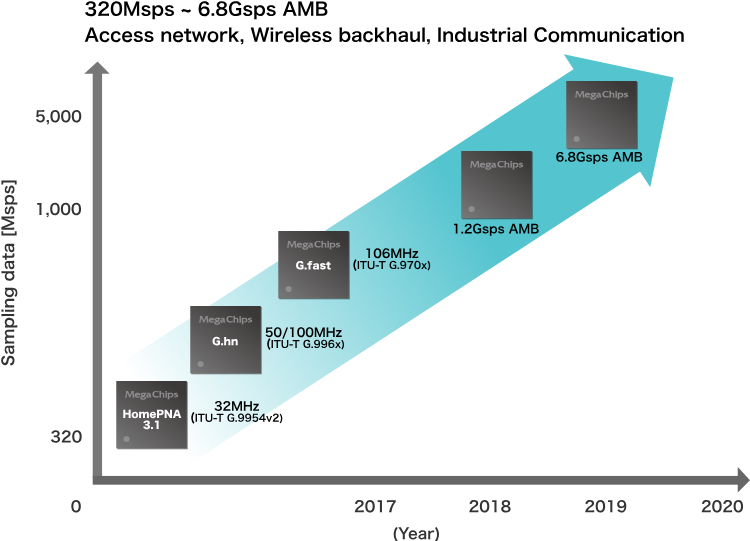

高性能・低価格を追求して開発されたメガチップスのAFE IPには、高性能 ADC、DAC、PGA(Programmable Gain Amplifier)、IAMP(Current Amplifier)、PLL、フィルターが実装されています。そのため、ASIC SoCはもちろん高性能汎用AFEチップにも適用可能です。過去10年間で 5,000万個超の高性能AFE 製品の出荷実績を持つメガチップスのテクノロジーは数多くの高速通信製品の中核を担っており、世界中のお客様から評価いただいています。

特徴

- 12bits 200Msps~1200Msps ADC

- 12bits 200Msps~1200Msps DAC

- 低ノイズPGA: ゲインレンジ-12dB~+48dB

- 低ジッタPLL

対応スタンダード例

- G.hn ITU-T Recommendation G.9960

- G.hn-mimo ITU-T Recommendation G.9963

- G.fast ITU-T Recommendation G.9700

- HomePNA3.1 ITU-T Recommendation G.9954

- HD-PLC

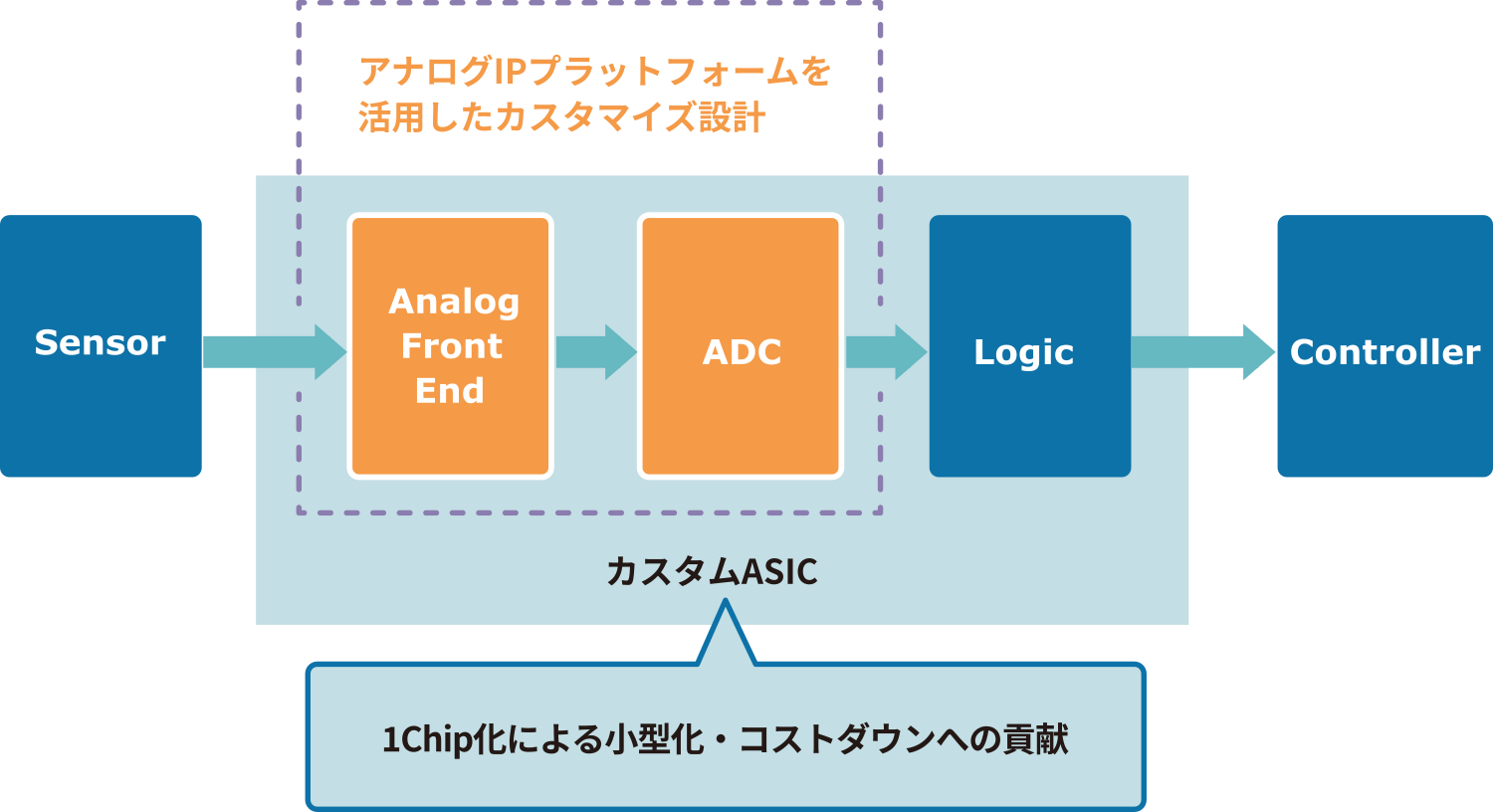

FA向けアナログIPプラットフォーム

メガチップスは、産業機器に必要な各種アナログマクロの開発プラットフォームを整備しています。IO-Link Transceiver IPに加えて、センサーインターフェースに必要なADC、DAC、Clock Generator、LED Driverなど各種アナログマクロを保有し、これらをお客様のニーズに合わせてカスタマイズする開発プラットフォームにより、小型化、コストダウンに貢献していきます。

特徴

- IO-Link Specification Ver1.1.3準拠のDevice Transceiver IP

- ADC、DSC、OSC、LDO、LED Driver等、センサーインターフェース構築に必要なアナログマクロのラインナップ

- 小型化、コストダウンに向けたカスタマイズ設計

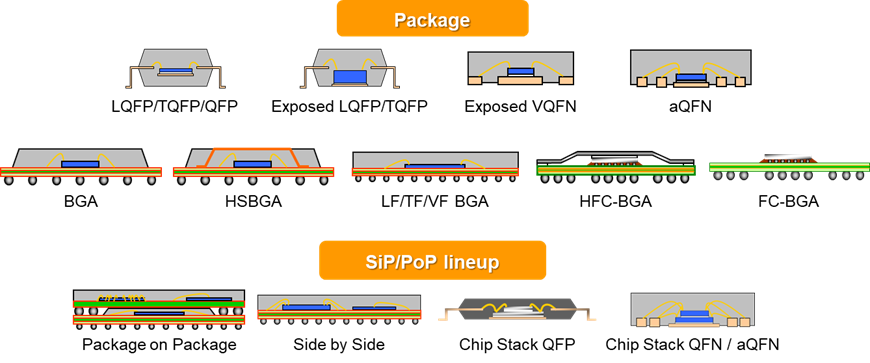

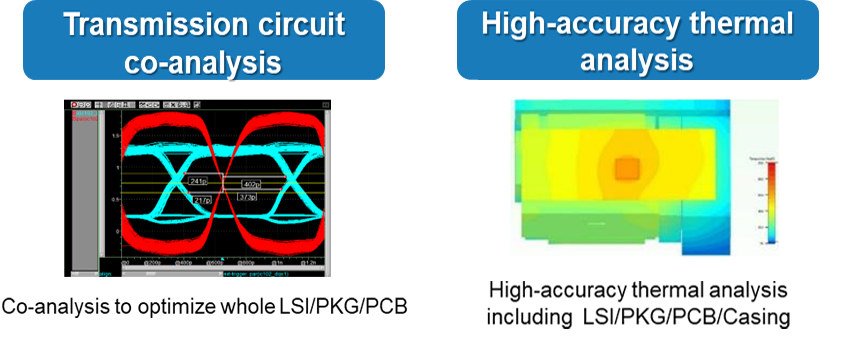

SI/PI解析に基づくLSI-PKG協調設計技術

メガチップスは、お客様のニーズに合わせた幅広いパッケージ(PKG)のラインナップに対応します。またメガチップスが保有するSignal Integrity / Power Integrity(SI/PI)解析、熱解析の技術を駆使し、LSIとPKGの協調設計を行いお客様に最適なソリューションを提供します。