ソリューション

FPGA・ASIC転換

FPGAをASICに転換することで量産コストの低減を実現します。

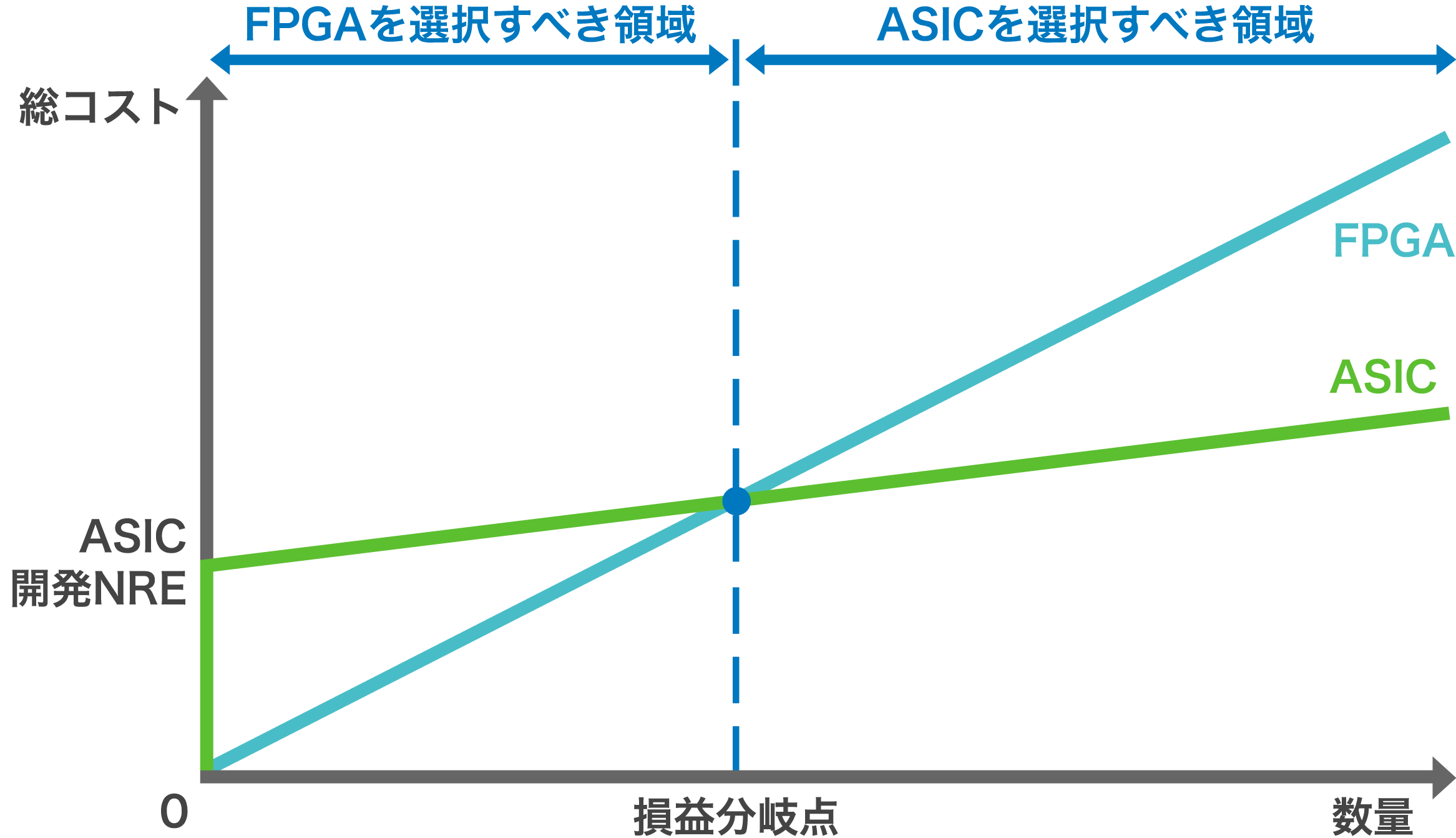

FPGAは、ASICと比べて初期コストを低く抑えられる半面、量産数量が多い場合はASICよりもコストが高くなります。コストを削減するには、必要な数量に応じてFPGAとASICのどちらかを選択するという判断が不可欠です。メガチップスは、お客様のFPGAからASICへの転換を最大限サポートします。

FPGAとASICの違い

FPGAをASICに転換する判断材料としては、コストだけなく消費電力も挙げられます。FPGAは近年、プロセスの微細化が進んだことにより、搭載可能な論理を大幅に増やし、動作周波数を向上させました。一方で、消費電力、特にリーク電力が増大し、FPGAが高熱になるという問題が生じています。近年のFPGAは動作周波数を上げることを最重要課題としており、ASICでは当たり前となりつつあるクロックゲーティング挿入や、Multi-Vth最適化などの低消費電力設計を行うことができないためです。FPGAを適用すると、ヒートシンクをパッケージに載せるなどの熱対策が必要となり、製品の量産コストがさらに増加する場合があります。

ASICは、同程度のプロセスのFPGAと比べるとゲート使用効率が高いため、FPGAからASICへの転換や低消費電力設計手法の適用によって、消費電力を低減することができます。加えて、FPGAの動作速度はASICよりも遅いため、一世代前のプロセスのASICでもFPGAの動作速度に対応可能です。FPGAを一世代前のプロセスのASICに転換することで、消費電力を3分の2以上削減することが期待できます。

FPGAとASICを比較した場合のメリット・デメリットは、下表の通りです。初期コスト・Time to Market・ECOのインパクトの観点では、FPGAを適用した方が良いといえます。しかし、量産数が多い場合は、ASICを選択した方がコスト削減となります。以下グラフでFPGAとASICの数量・コストのバランスを示します。

FPGAとASICの比較

| Category | Item | FPGA | ASIC |

|---|---|---|---|

| 初期コスト・Time to Market | 論理設計期間 | 〇 | 〇 |

| レイアウト期間 | 〇 | △ | |

| 製造期間 | 〇 | × | |

| レチクル費用 | - | × | |

| 開発リスク・ECOのスケジュールインパクト | テープアウト後の論理修正によるイタレーション期間 | 〇 | × |

| テープアウト後の論理修正による追加のレチクル費用 | - | × | |

| パフォーマンス・コスト・その他 | 動作周波数 | △ | 〇 |

| 集積度 | × | 〇 | |

| 低消費電力設計 | × | 〇 | |

| カスタム(自由度) | △ | 〇 | |

| パッケージ自由度 | △ | 〇 | |

| チップ単価 | × | 〇 | |

| Business Continue Plan | × | 〇 |

損益分岐点を境にFPGAとASICが逆転

メガチップスのソリューション(開発手法と支援内容)

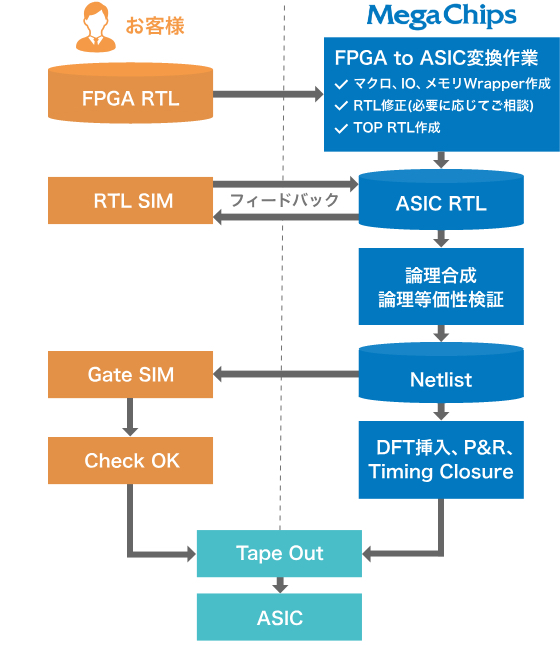

メガチップスは、既存のFPGA資産とASIC転換についての要望をヒアリングし、最適なASIC転換ソリューションを提案します。FPGAとのピンコンパチブルにも、可能な限り対応します。

以下は、FPGAをASICに転換するフロー例です。さらにお客様の負担を減らすため、論理シミュレーションを当社が担当することも可能です。

開発プロセス

FPGA→ASICコンバージョンフロー例

お客様のメリット

当社は、ASICの設計開始から量産に至るきめ細かいサポート体制を構築しており、お客様から好評いただいています。FPGAの資産を使ってASICに転換し量産するまで、お客様の負担を最小化しつつ、当社で十分な作業と検証を行います。お客様に提供する主なメリットは以下の通りです。

メリット

- FPGAをASICに転換することにより、お客様の負担は最小限でありながら量産時のコスト削減を実現します。

- すでにボード設計が完了している場合は、ASICをFPGAとピンコンバチブル対応することにより、ボード設計の修正が不要です。※

- FPGAをASICに転換することにより、消費電力を削減でき、その結果、システムの消費電力を低減できます。

- FPGAでは必要であったヒートシンクなどの熱対策が不要となり、コスト削減が期待できます。

※ 技術的な検討を行った結果、ピンコンパチブル対応不可と判断する場合があります。また、バイパスコンデンサ追加などの改良をお願いする場合がございます。

開発事例

開発事例1:OA用途

| Item | FPGA | ASIC (55nmプロセス) | 効果 |

|---|---|---|---|

| 開発費 | 3,000万円 | 8,000万円 | 損益分岐点:83K個 |

| 単価 | 1,000円 | 400円 | |

| 周波数 | 200MHz | 200MHz | FPGAコンバージョンのため同等 |

| 消費電力 | 1300mW | 400mW | 70%カット |

| 開発期間 | - | Final RTLからES納入まで4ヶ月 | - |

開発事例2:FA用途

| Item | FPGA | ASIC (28nmプロセス) | 改善率 |

|---|---|---|---|

| 開発費 | 5,000万円 | 20,000万円 | 損益分岐点:15K個 |

| 単価 | 10,000円 | 350円 | |

| 周波数 | 200MHz | 500MHz | 2.5倍UP |

| 消費電力 | 1000mW | 400mW | 60%カット |

| 開発期間 | - | Final RTLからES納入まで8ヶ月 | - |

お客様の声

- ASIC化の事前検討で想定外のRTLの問題が見つかったものの、御社のきめ細かいサポートにより、スケジュール通りテープアウトすることができました。

- 次期機種に向けたASICが立ち上がるまで、数年間はFPGAを搭載して量産することを考えていましたが、FPGAからASICへの転換によるコスト削減の提案を御社から受け、ASIC転換に舵を切ることができました。大変素晴らしい提案だったと思います。