ソリューション

5G・光通信向け開発

5G RU ASICソリューション

5G RUをより低消費電力、低コストに

5G RU機能をFPGA + ディスクリート AFEを使って実現することは、time to marketの要求を満たすためには最適な解ですが、出荷数量の増加に伴い消費電力やコストの問題が顕在化します。

メガチップスは、長年にわたるASICビジネスで培ったFPGAからASICへの変換の経験と高速・低消費電力のデータコンバーター開発・実装の経験を活かし、お客様にハイボリュームに最適な低消費電力、低コストの5G RU ASICソリューションを提供します。

アプリケーション: 5G RU

- サブ6G and/or ミリ波マクロセル

- サブ6G and/or ミリ波スモールセル

- ミリ波スマートリピーター

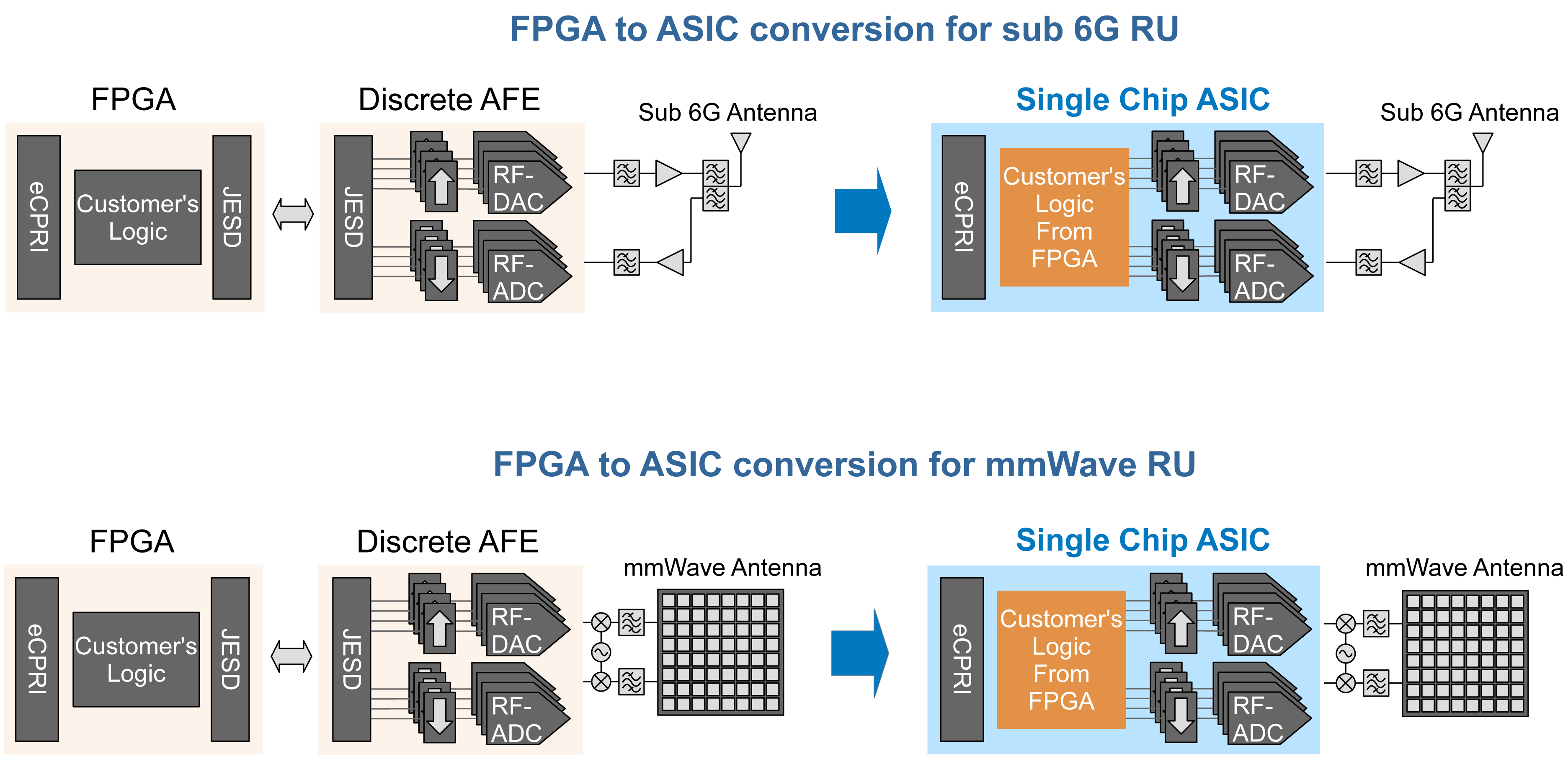

FPGAからASICへの変換

パフォーマンスを損なわないスムーズな変換を実現

5G RU FPGAからASICへの変換

メガチップスの5G RU ASICソリューションは、高価でパワーハングリーなFPGAを、お客様のシステムのパフォーマンスを損なうことなく、ASICに変換することを可能にします。これにより、システムパフォーマンスの犠牲なく、お客様のシステムのコスト効率を高め、かつ消費電力を最大55%節約できます。

メガチップスはこの変換を低リスクで行うために、2段階のアプローチを推奨しています。

ステップ1:アナログテストチップの開発

この変換の成功の鍵は、アナログIP、特に高速データコンバーターがお客様のシステムで所望のパフォーマンスを実現できるかを開発初期段階で見極めることです。この見極めを可能にするため、豊富なデータコンバーター IPラインアップの中からお客様の要求仕様にミートするサンプリングレレート、バンド幅、変換方式のIPをカスタマイズしたアナログテストチップを開発し、このテストチップを使用してアナログIPの性能/特性をお客様のシステム上で評価することを推奨しています。これにより、最終チップでの予期しないパフォーマンスのリスクを最小限にすることが可能になります。

ステップ2:最終的なシングルチップ開発

アナログテストチップを用いたシステムレベル評価でアナログIPの性能/特性が確認できれば、FPGAのユーザーロジックとアナログIPを統合し、シングルチップ化したASICを開発します。これが最終的な5G RU ASICになります。

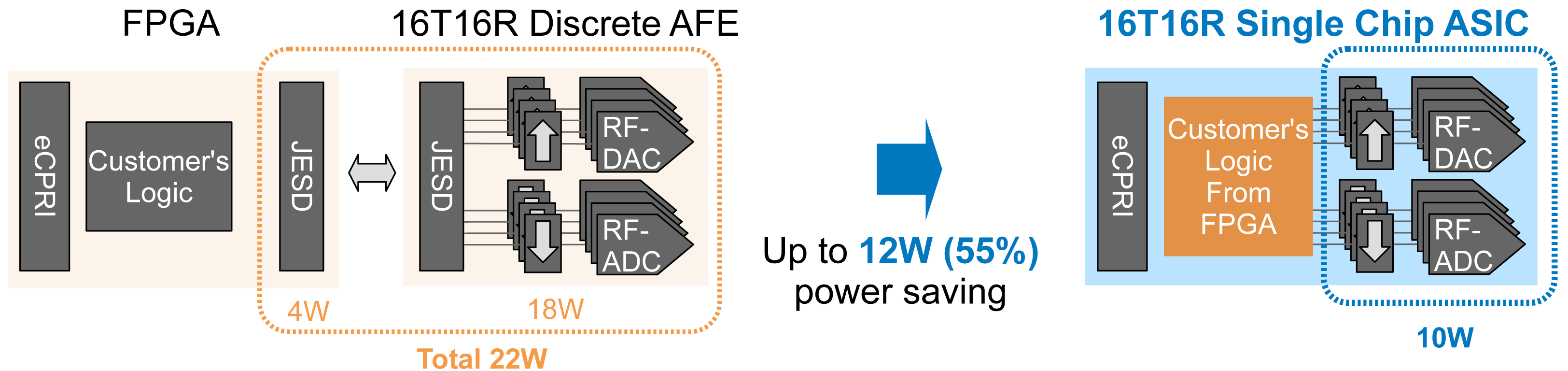

消費電力を最大55%削減

ディスクリートAFEとFPGA間のデータバスは、総消費電力の多くの部分を占めており、かつMIMO数の増加に伴い、このデータバスの消費電力は増加傾向にあります。メガチップスのFPGAからシングルチップASICへの変換は、このデータバスを排除することにより、消費電力を最大55%削減できます。

| 16T16R DISCRETE AFE + FPGA JESD | 16T16R SINGLE CHIP ASIC IN 7 NM | ||

|---|---|---|---|

| FPGA JESD | 4W (250mW x 16 ch) | AFE | 10W |

| Discrete AFE | 18W (4.5W x 4 chips) | ||

| Total | 22W | Total | 10W |

利用可能なテクノロジーノード

TSMC: 28nm, 16nm FFC, 5/7nm(計画中)

GF: 22nm FDSOI, 12nm FDSOI(計画中)

包括的な5G RU ASIC開発サポート

製品定義から量産まで

メガチップスは、ASICの実装や量産対応といった一般的なASIC開発サポートに加えて、ASIC開発の経験が少ないお客様向けに、製品定義やFPGA開発などといった上流設計・開発のサポートも提供しています。

この包括的なサポートにより、ASIC開発経験の少ないお客様も付加価値のあるASICの開発が可能になり、その結果お客様がより競争力のある製品を開発することをサポートします。

光通信ASICソリューション

AI、ビッグデータ、IoT等の進展とともに増加の一途にあるデータ通信に対応するため、基幹系およびメトロ、アクセス系のネットワークから、さらには家庭内ネットワーク、端末に至るあらゆる階層で光通信の需要が高まっています。メガチップスは、これら光通信の分野において、高速インターフェースとASIC集積化のソリューションをご提供します。

PON SerDes技術

メガチップスは、とりわけ光アクセス系のPassive Optical Network(PON)に向けた高速シリアルインターフェース(SerDes)に15年以上の製品実績を有しています。その間に蓄積してきたバーストモードCDR(Clock Data Recovery)SerDes技術は、幅広いPONスタンダードに対して柔軟に対応することが可能であり、国内外で幅広く使用されています。

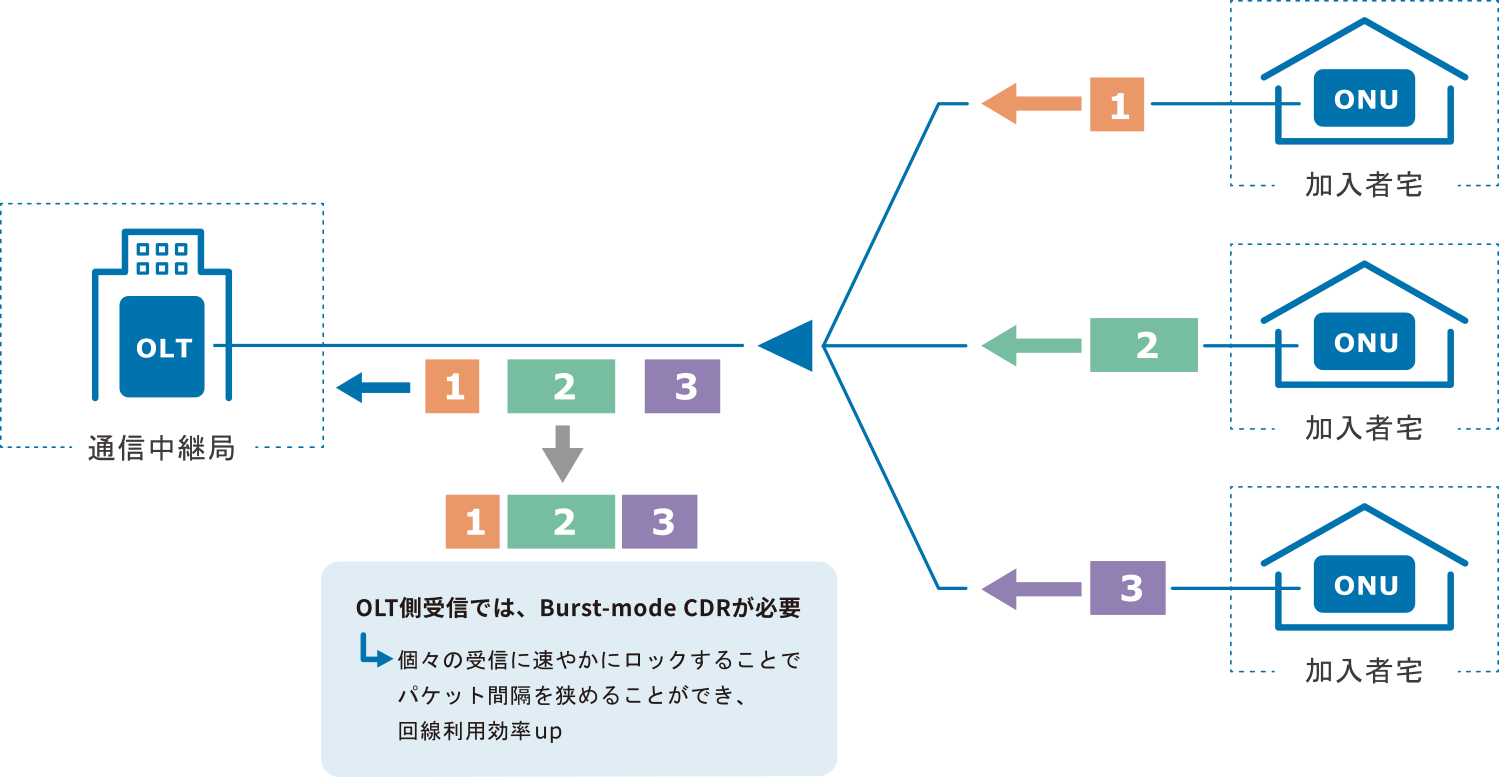

PON上り信号(upstream)の通信イメージ

PONは、通信中継局と多数の加入者宅の間を光スプリッタで分岐して繋ぐ1:Nのネットワークです。そのため上り信号(upstream)側は、複数の加入者からの信号を時間分割して一つの中継局で受信する必要があります。中継局側の通信装置(OLT: Optical Line Terminal)では、回線利用効率を高めるために異なる加入者からの個々の信号に速やかにロックできるバーストモード対応のクロック再生回路を備えたSerDes技術が求められます。メガチップスはバーストモード対応のPON SerDesの製品化に早くから取り組み、国際標準化にも積極的に参画してきました。

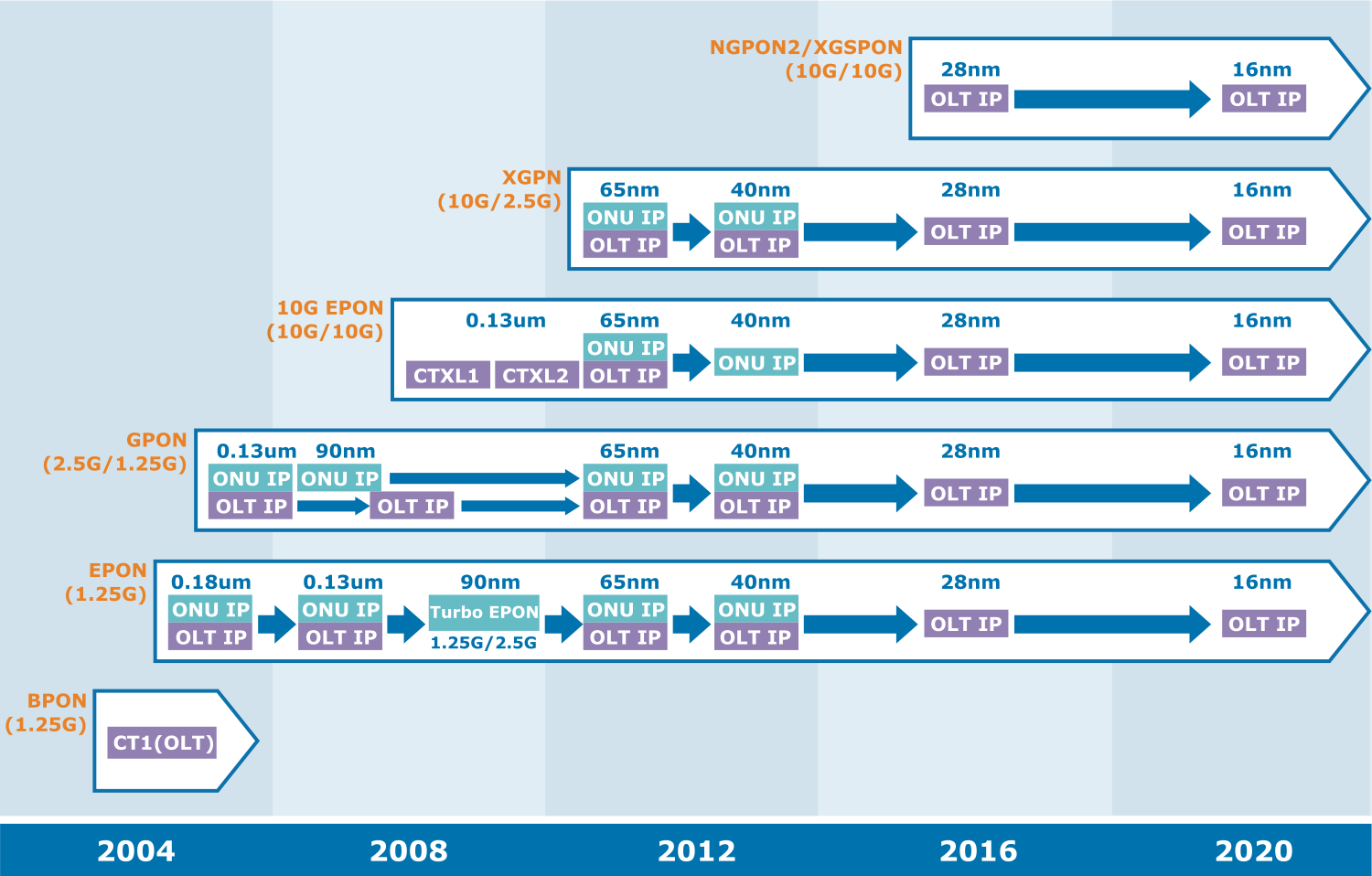

メガチップスのPON SerDesヒストリー

メガチップスはこれまでに中継局側OLT(Optical Line Terminal)、加入者宅側ONU(Optical Network Unit)の両面で幅広いPONスタンダード向けに多くの製品を提供してきました。

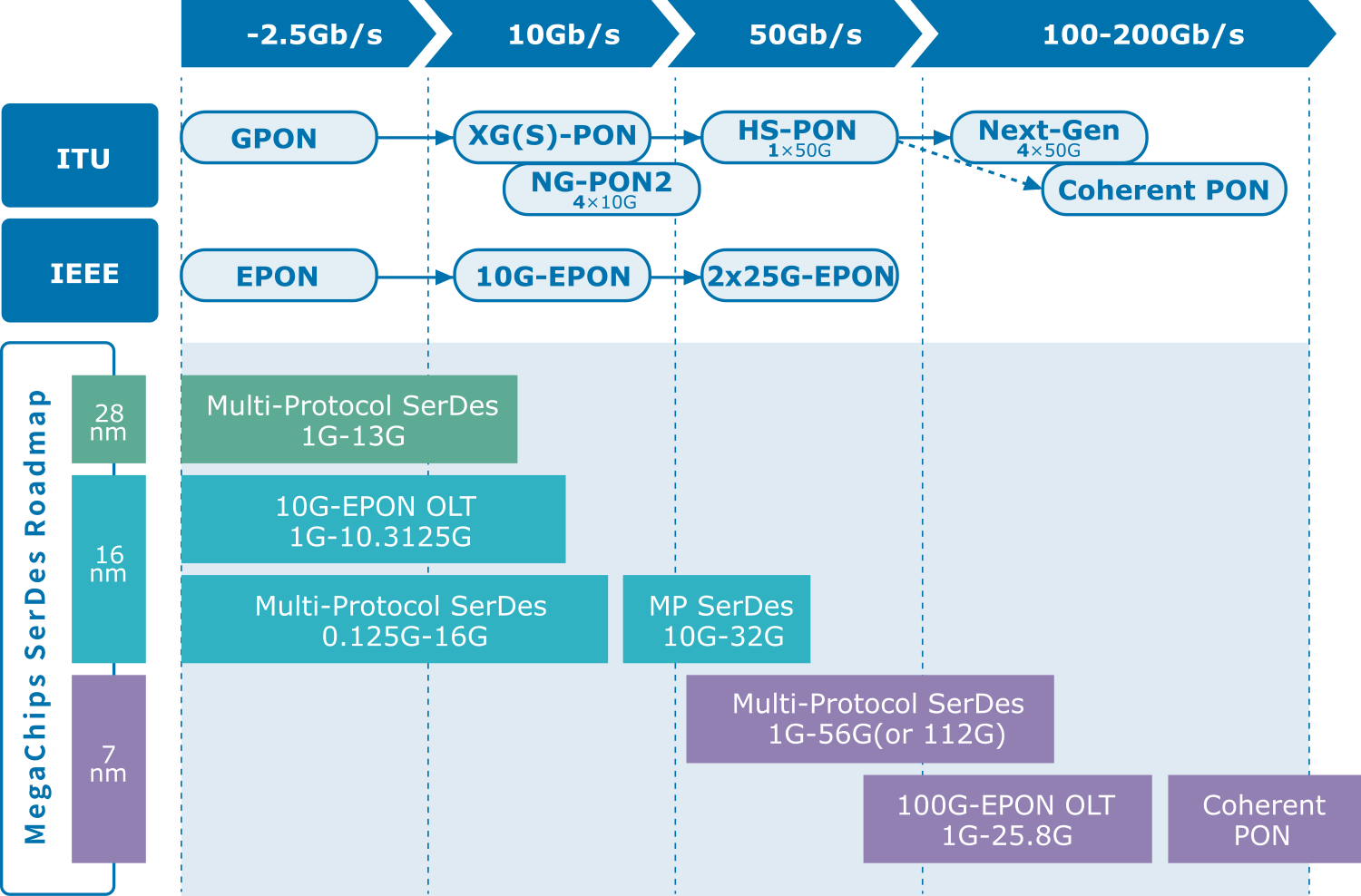

PON規格動向への対応

メガチップスはPONスタンダードの動向を注視し、今後もお客様のニーズにお答えするASIC製品をご提供します。