開発手法・フロー

協調設計

メガチップスは、システムをより確実に正常動作させる手法として、協調設計フローに基づいたASIC開発にも対応しています。

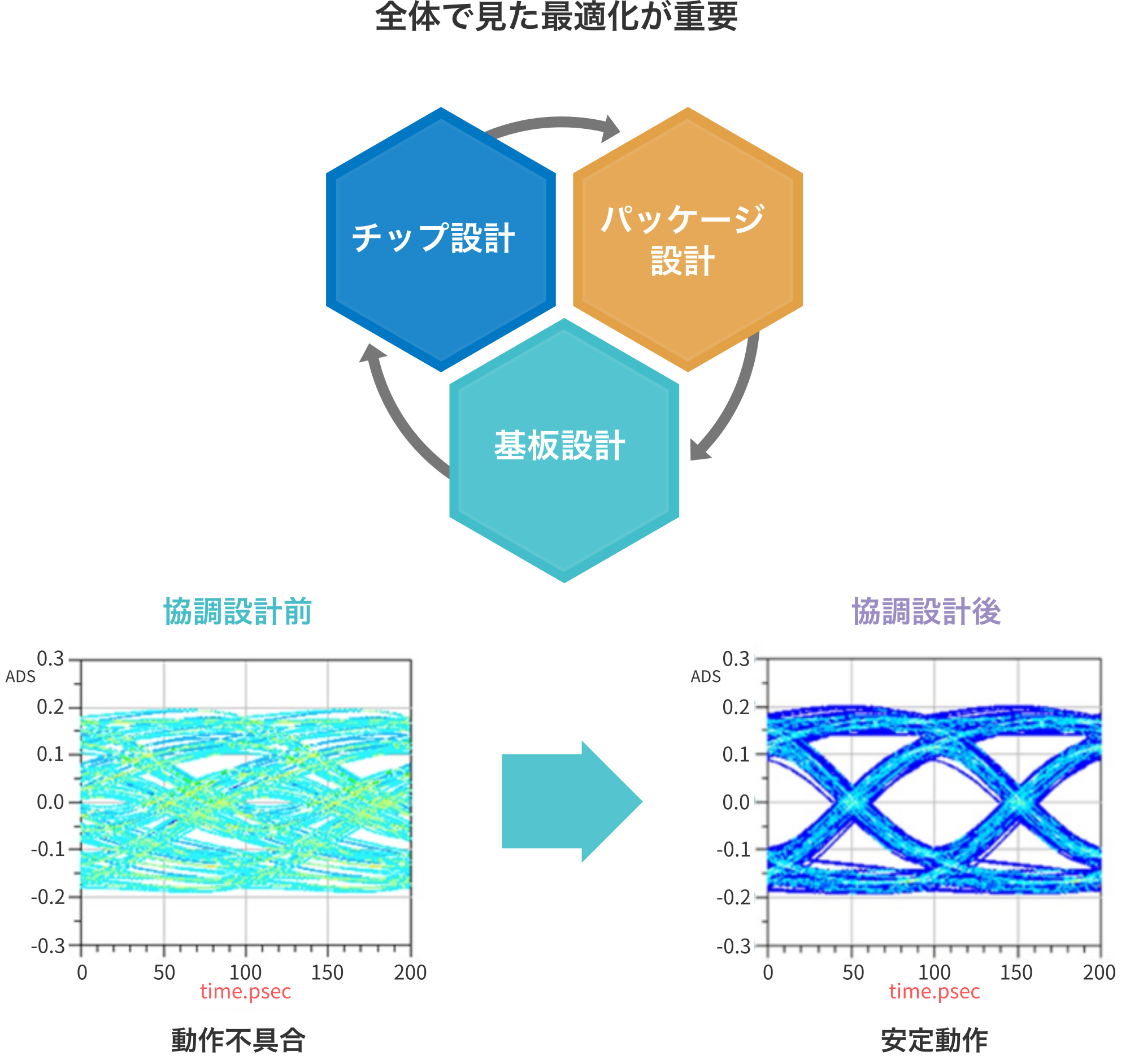

近年、転送レートの高速化、実装技術の複雑化などが進み、パッケージ設計の最適化だけではシステムを正常動作させることが困難になりつつあります。このため、「LSI・パッケージ・基板」を全体で最適化するLPB協調設計が必要とされており、当社ではこれらを全体最適化するために最新CAEツールを駆使した統合解析フローを構築しています。

協調設計の支援内容

- チップ、パッケージ、プリント基板それぞれの設計フローと並行してSIPI、熱、応力の観点から協調解析を行うことにより、Front Loading(開発初期段階からの課題抽出と対策実施)が可能

- Quality(リメイク低減、システム品質向上)、Cost(部品削減、工数削減)、Delivery(システム開発期間短縮)といったお客様システムにおけるQCD最適化を実現

- お客様ご自身での解析要望にお応えして、SPICEネットリスト、IBISモデル(AMI含む)、パッケージモデル、電源モデルを提供

確実・安定的な動作状態を実現

お客様の全体設計の最適化が困難な要因としては以下が挙げられます。

- 伝送レートの高速化(1Gbps以上)によるタイミングマージンの減少

- Bit数増大によるSSN、Xtalkの影響の顕著化

- 低電圧化による許容ノイズマージンの減少

- チップ動作状態を考慮した熱解析モデルの構築が必要

- 熱、応力解析値のチップ・パッケージ設計へのタイムリーなフィードバックが必要

メガチップスのチップ・パッケージ・プリント基板協調解析手法により、これらの課題をクリアにして、より確実に安定した動作状態を実現することが可能となります。

パッケージの製造の詳細については下記をご覧ください。