開発手法・フロー

DFT(テスト簡易化設計)

IoTの時代を迎え、自動車の電子機器搭載が増えるなか、テスト高品質化はより重要な課題となっています。また、回路の大規模化・プロセスの微細化・高速動作化に伴い、ASICはますます複雑となり、DFT(Design For Test)に求められる要求と設計難易度が高まっています。

当社には、テストおよび先端のEDAツールに精通している専門DFTエンジニアが多数在籍しています。各種プロジェクトに応じた最適な設計を行うことで回路規模・設計TATへの影響を最小限に抑えるとともに、高品質なテストによる低不良発生率を実現しています。

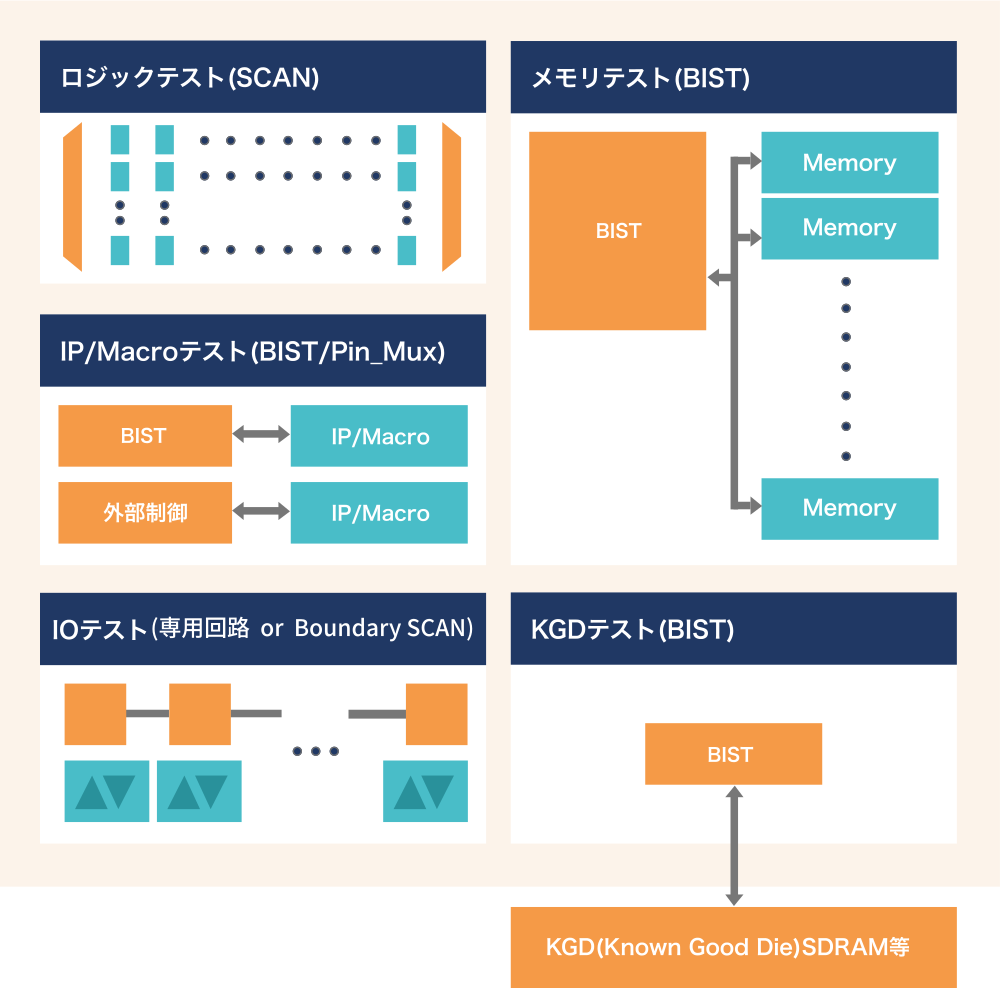

DFT設計の概要

標準パーツを組み合わせてプロジェクトごとに最適なDFTを構築

メガチップスのDFTの特徴

特徴1 高品質テスト対応

当社では、高品質なテスト実現に向けて、以下の技術を採用しています。

■オンチップPLLを用いた高速クロックテスト

高速クロックの準備、クロック・リセット経路に関して、お客様側で事前にテスト用の回路を修正する必要はありません。

■高位Fault model適用

必要に応じて、SCAN時に以下の高位Faultも考慮することで、低不良率を実現しています。

- Cell-Aware (Cell内部の故障ノードを考慮)

- Bridge Fault(配線shortを考慮)

- Path Delay (クリティカルパスを考慮)

Memory BISTでは、FinFETに対応したアルゴリズムを適用し、低不良率を実現しています。

特徴2 レイアウトへの負荷軽減

高度なDFT回路の挿入は、エリア増加、Timing収束、テスト時の消費電力増加などの悪影響を招きます。これらを最小限にするために、SCAN挿入やメモリBIST挿入においては、レイアウトを考慮したDFT挿入を実施しています。また、ノーマルモードとテストモードのクロック混載についても、レイアウト担当者と綿密な計画を立て、最適な回路制御やCTS挿入を実現しています。

特徴3 専用のデバッグ解析ツールで不良箇所と要因の分析を迅速化

テストの高度化に伴い、Failログからの不良箇所特定が難しくなっています。当社は、専用のデバッグ解析ツールを用いることで、追加の解析用パターンを用意することなく、量産テストのFAILログから確度の高い故障箇所を抽出することができます。これにより、物理解析に費やす時間が減少し、フィールド不良サンプルに対する短期間での原因分析に貢献します。