開発手法・フロー

サブシステムの活用

当社は、CPUや各種IPの豊富な開発実績を活かし、それらを組み合わせたプラットフォームとして、高性能、低消費電力なサブシステムを開発、提供しています。お客様がこのサブシステムを活用することにより、煩わしい開発の手間が低減し、自社の差別化技術開発に注力していただくことが可能となります。

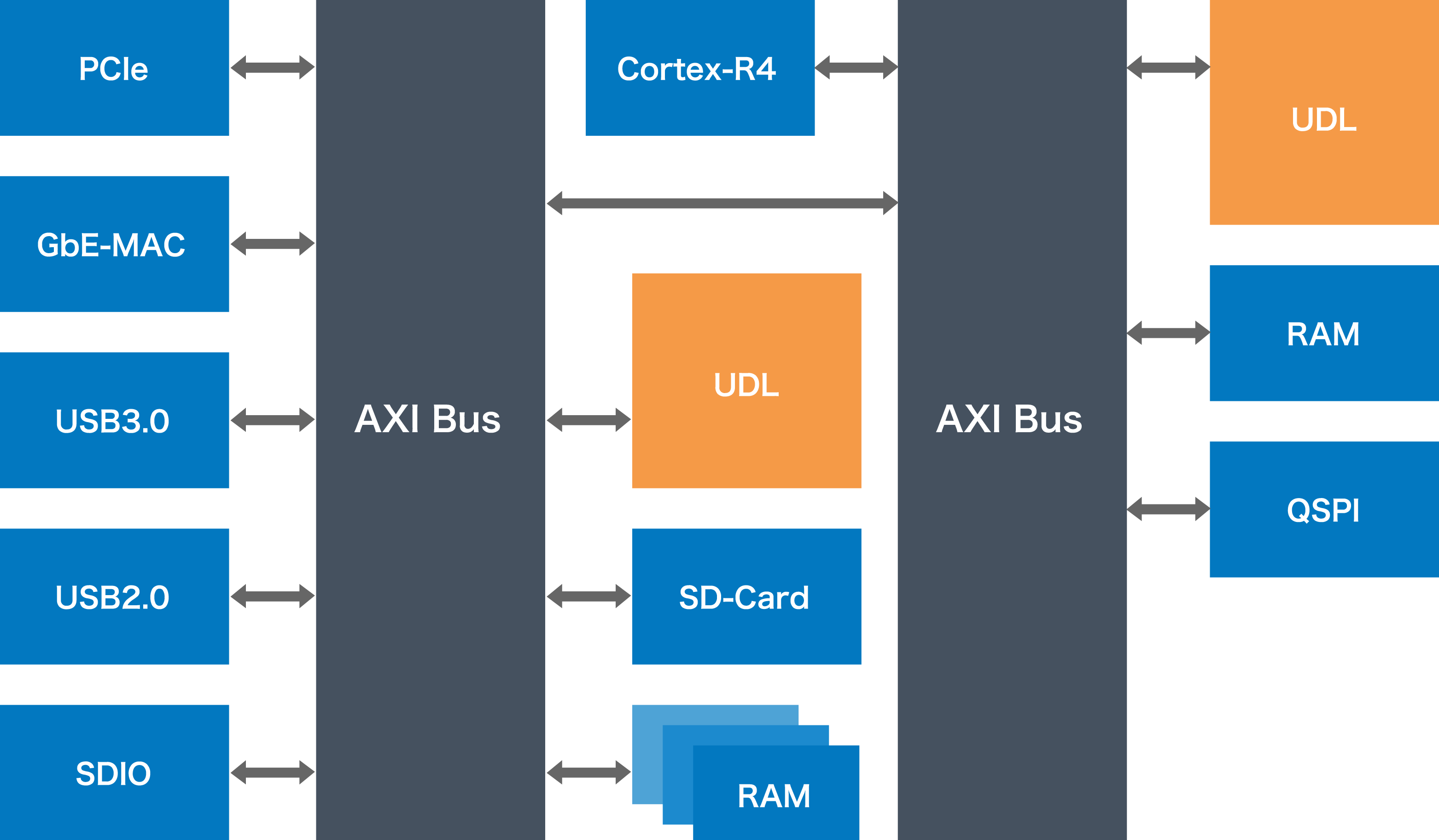

CPUサブシステム

これまでに100プロジェクト以上のCPU搭載のSilicon実績があります。お客様の要望に最適なCPUサブシステムを提供します。また、要望に応じてCPUサブシステムをカスタマイズし、ソフトウェアおよび検証環境とともに提供します。

機能概要

Arm® Processor(Cortex-A系/R系/M系)、RISC-V®、DMAC、USB、PCIe、GbE-MAC、SDIO、HDMI、各種ペリフェラルおよびセキュリティIP に加え、AXI Bus パフォーマンスやパワーマネージメントに関しても、お客様とともに最適なカスタマイズを行います。

CPUサブシステム例

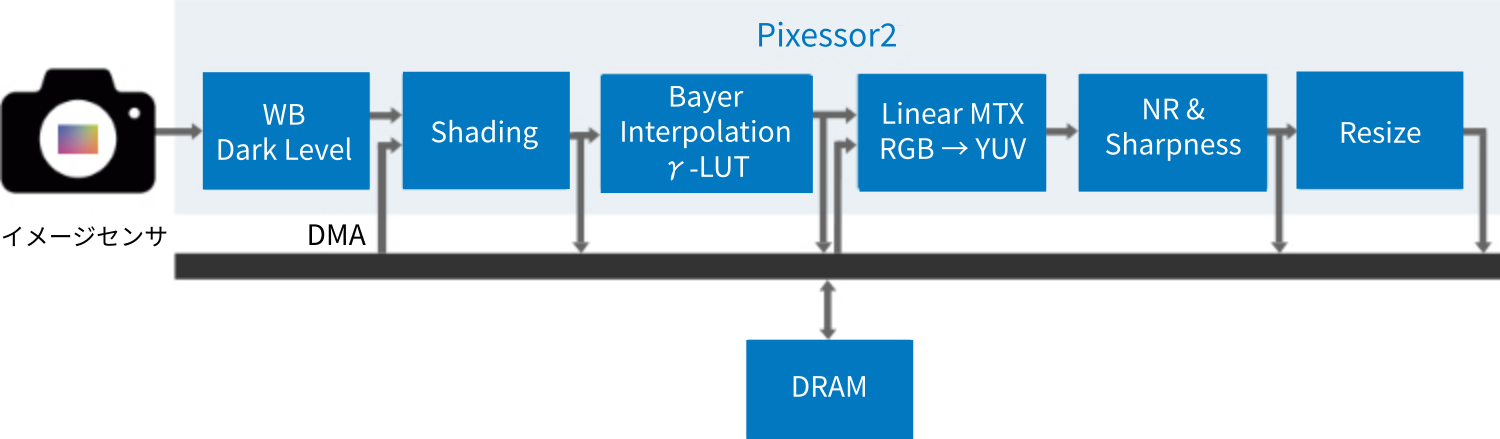

ISP(Imaging Signal Processor)サブシステム

イメージシグナルプロセッサ“Pixessor2™”は、当社が独自に開発した2次元画像用の高速処理エンジンで、複数の一眼レフカメラおよびスマートフォンメーカーに採用されたISPです。要望に応じてカスタマイズを行い、高精細、高性能なサブシステムとして提供します。

機能概要

Pipe-Line Processingをベースとしたハードウェアで高性能、高速処理を実現するとともに、DSPのようなスケーラビリティとフレキシビリティも兼ね備えています。また、Coring、各種フィルタ処理は、当社独自のアルゴリズムである線分検出を備え、高精細、ノイズ低減を実現します。

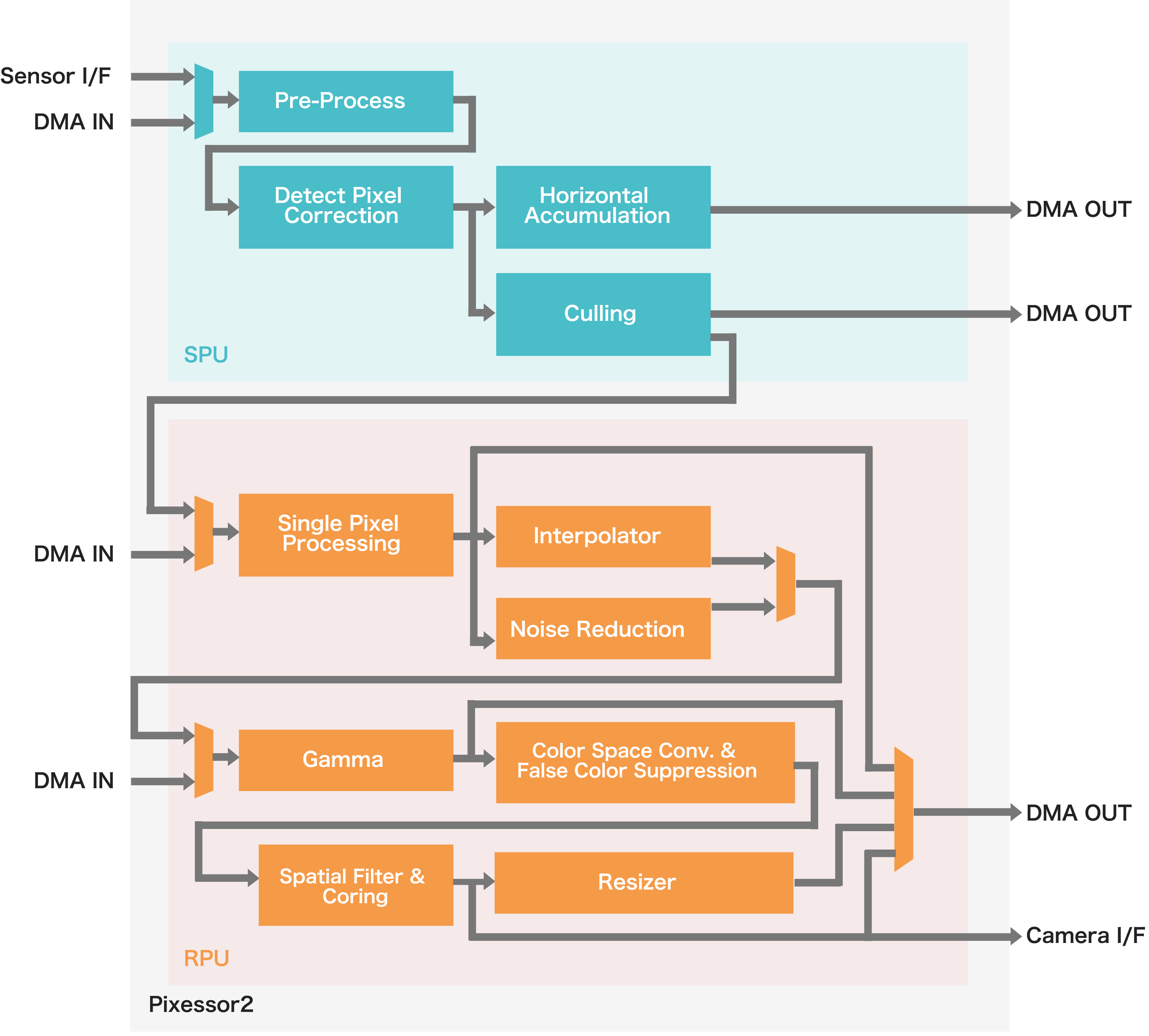

Pixessor2™ブロック図

主な特徴

- Defect Pixel Correction

- 2D Color Enhancer

- Shading Correction

- Bad Pixel Correction

- Linearization Correction

- Dark Level Correction

- Coring

- Dark Noise Removal

- Affine(Distortion Correction, Fisheye Panorama Correction)

ISPサブシステムは以下「カメラ信号処理技術(Pixessor-IP)」および「歪み補正(Affine) IP」で構成されています。

1.カメラ信号処理技術(Pixessor-IP)

Pixessor-IPは、デジタルカメラなどのRAW(Bayer)データを⾼速に画質処理するIPです。画像データをメモリから読み出し、歪み補正して、メモリへ出力します。本IPは、他社デジタル一眼レフカメラやスマートデバイスへも搭載されています。

主な特徴

- カメラ画像処理に必要な処理(デモザイク処理、ホワイトバランス処理、ゲイン処理など)を多数のハードウェアブロックで実現

- 個々の処理ブロックをフレキシブルに組み合わせてリアルタイムに処理

2.歪み補正(Affine) IP

Affineは、当社が独自に開発した歪み画像補正用IPです。画像データをメモリから読み出し、歪み補正して、メモリへ出力します。

機能概要

レンズ歪みによって、樽型、糸巻型に歪んだ画像を補正します。パラメータを変更することによって、トリミング、連結、回転、反転、拡大、縮小などを組み合わせた柔軟な処理が可能です。

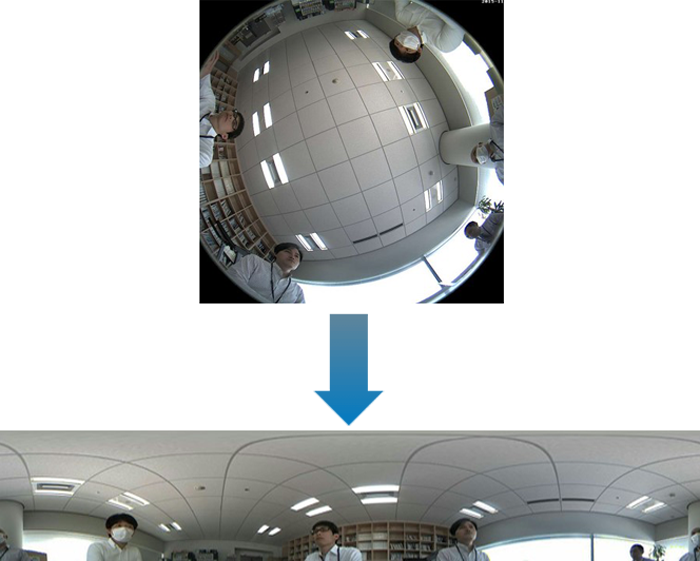

補正イメージ図(例:魚眼パノラマ補正)

歪み補正

魚眼パノラマ補正

主な特徴

- 歪み補正

- トリミング、連結

- 回転、反転

- 拡大、縮小

- 魚眼パノラマ補正

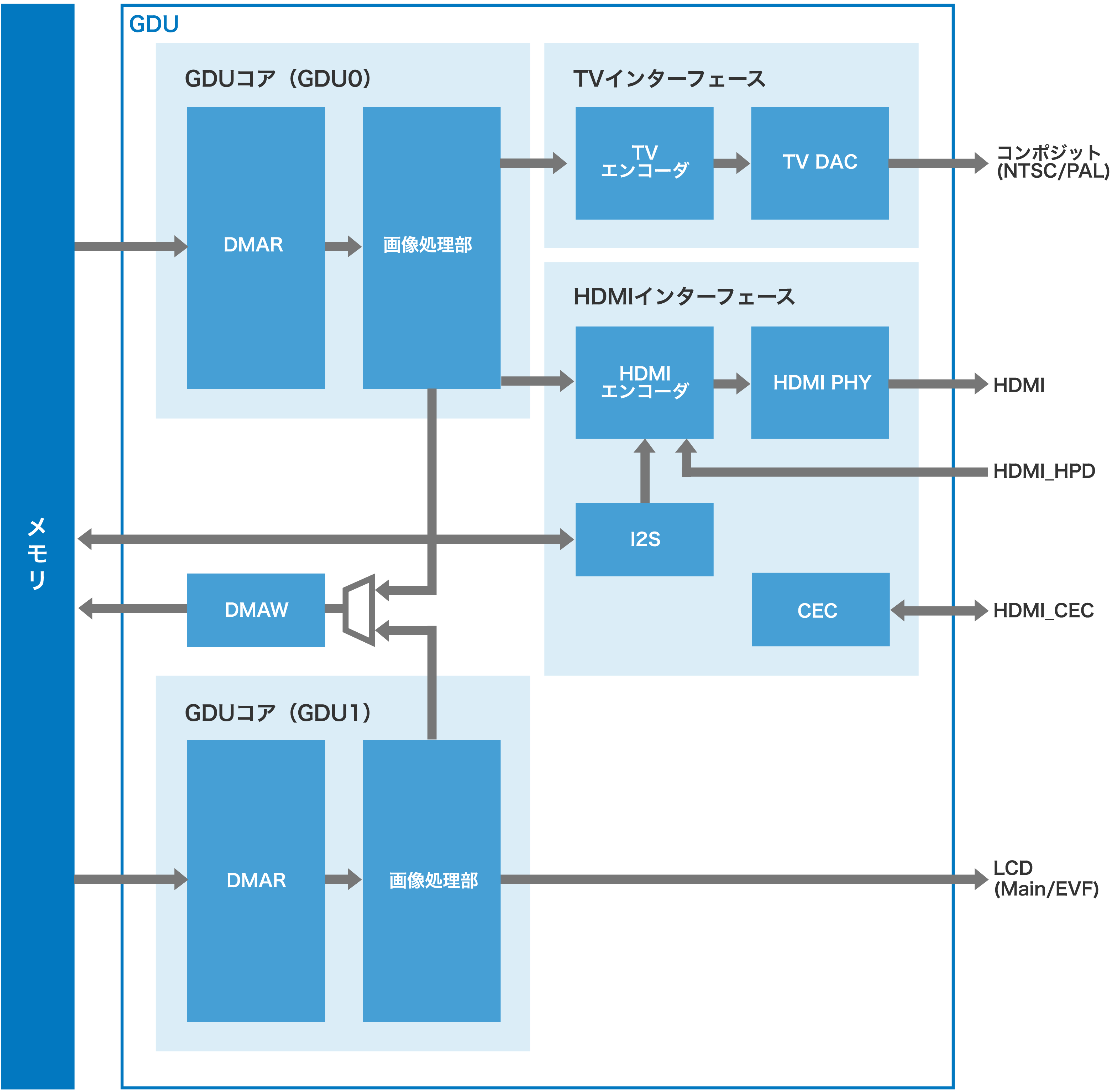

GDU(Graphic Display Unit)サブシステム

GDUは、当社が独自に開発した画像表示用IPです。複数の画像データをメモリから読み出し、LCDやHDMIといった外部デバイスに出力します。

機能概要

一般的な表示機能(レイヤー機能、アルファブレンド機能、ウィンドウ機能、オートリカバリ機能)を搭載しています。さまざまな同期信号が生成できるため、必要な用途のI/Fにフレキシブルに対応します。また、各種画像補正を行うことも可能です。

GDUブロック図

主な特徴

- 矩形読み出し

- 水平/垂直フリップ

- 180°ローテーション

- パディング

- ゼブラパターン表示

- ブリンクパターン表示