開発手法・フロー概要

メガチップスの開発フローは、先進EDA技術とデザインキット、豊富な経験に裏付けされた設計サービスを融合させており、お客様にとって最適なデザインを短期間で実現することができます。日々進化と改良を重ねながら、大規模化かつ複雑化するASIC開発をあらゆる面からサポートしています。

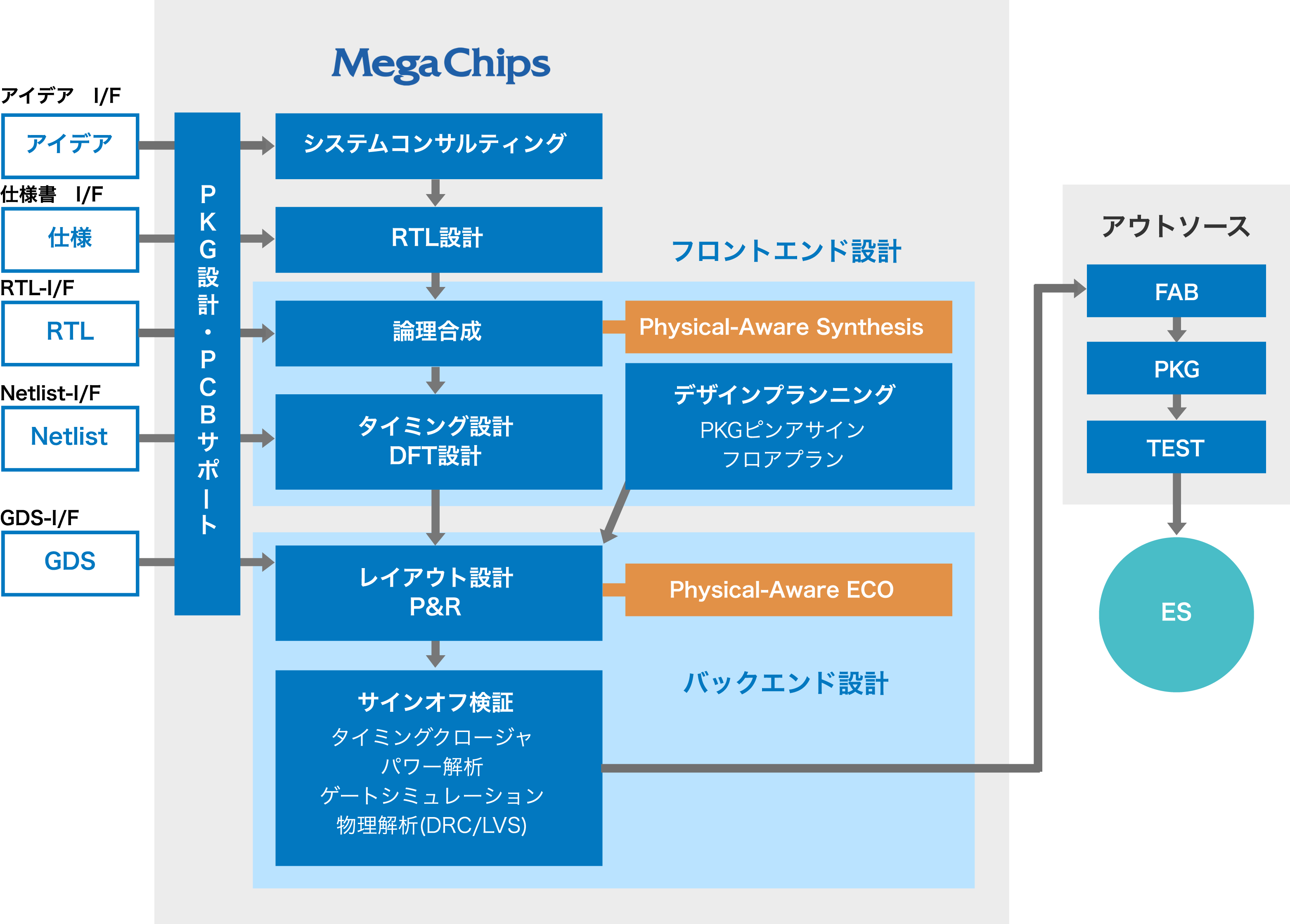

メガチップスの開発フロー

フロントエンドデザイン(論理設計・論理合成)

最新のEDAツールと最適化された設計環境、デザインキットを提供し、PPA(Power、 Performance、 Area)の最適なASIC開発を短期間で実現します。独自開発の補強ツール・ユーティリティによって各設計工程間をシームレスにつなぐとともに、ルールチェックを欠かさずミスの未然防止に努めています。

タイミングクロージャー

タイミングクロージャーはASIC設計フローの要です。正確なSDCを完成させるフローがあることで、ASICのインプリメンテーションが早く確実に収束し、開発TATを適切に保つことができます。

当社は、開発時にタイミングクロージャーの専任担当者をアサインし、複雑化するタイミング要求を確実に制約ファイル(SDC)に落とし込みます。さらに、丹念なレビューとバックエンド設計者とのスムーズな連携によって、お客様の要求を漏れなく正確にデザインに反映します。先進のPhysical-Aware手法を設計フローに取り込み、手戻りを最小化。大規模、複雑なデザインでもスケジュール通りの確実な開発を実現します。

SDC作成サポートユーティリティ

当社は、独自開発のSDC作成サポートユーティリティを用意しています。これにより、お客様が普段使い慣れているExcelフォーマットの入力ファイルからSDCを作成することが可能です。タイミング仕様を直感的に理解しやすいフォーマットで管理することにより、タイミング仕様に関するミスコミュニケーションを防止して、高品質なSDCを短期間で作成します。

バックエンドデザイン(物理設計・検証)

回路の大規模・複雑化に伴って、フラットレイアウトでは設計期間の長期化が顕著となっており、階層レイアウトの必要性が高まっています。業界最先端のEDAツールと当社の豊富な経験や実績を活用することで、回路の階層分割とマッピング、階層レイアウトブロック間の信号やIOとの接続、信号の流れを考慮したフロアプラン、ブロック単位のP&R技術などを実現し、長期化のリスクを伴う設計工程、設計期間を大幅に改善、短縮しています。

Physical-Aware Synthesis/Physical-Aware ECO

トランジスタの微細化に伴い、物理情報を考慮した設計が、後戻りのない最適なPPA実現のカギとなっています。当社はPhysical-Aware Synthesis/Physical-Aware ECOを開発フローに取り入れ、収束困難なデザインに対しても早期タイミング収束を実現しています。

Physical-Aware Synthesisは、合成時に物理情報(配置、配線)を考慮し、P&R以降に判明するタイミング違反箇所、配線混雑といった問題点を合成フェーズで精度よく見積もり、改善します。収束困難な問題点をRTL設計に早期フィードバックすることが可能です。

Physical-Aware ECOは、既存セルの配置を考慮することで高効率の自動タイミングECOを実施、イタレーションを削減して早期タイミング収束を実現します。

自動論理修正ECO

テープアウト直前に複雑な論理修正が発生すると、大幅な開発期間の見直しにつながりかねません。当社では、EDAツールを用いて論理修正ネットリストを自動生成し、論理合成や再レイアウトまで戻らずに、ECOで対応することが可能です。修正に伴うスケジュールインパクトを最小限にとどめます。