Development Method and Flow

FPGA Prototyping Service

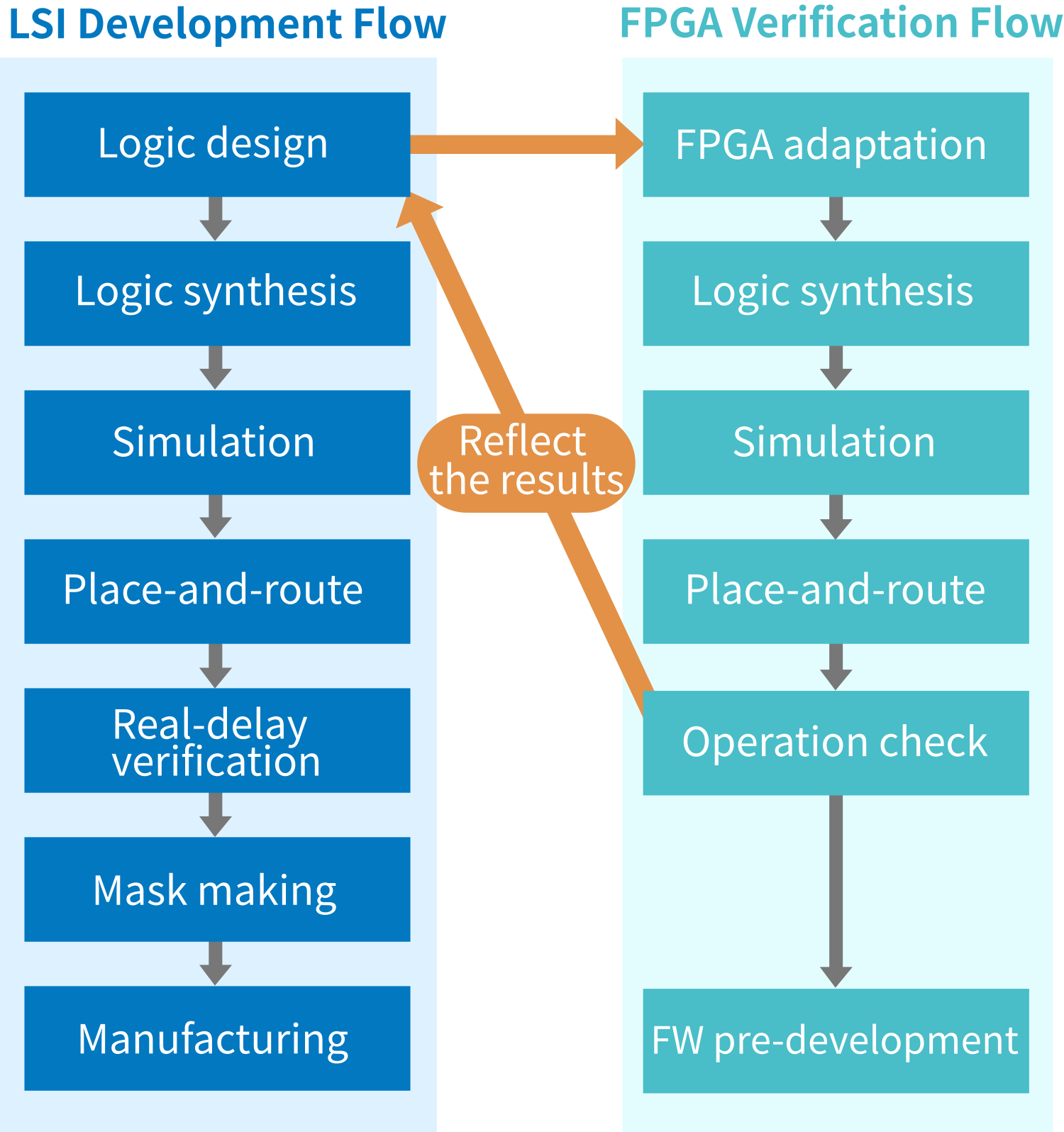

FPGA Prototyping Service builds a platform including customer-designed circuits in our subsystem and it supports detailed verification and software pre-development. By implementing equivalent circuits, such as ASICs in FPGAs and other devices, and evaluating operation, the functional evaluation and software pre-development can be performed before the ASIC is completed, thus enhancing ASIC quality and shortening the development period.

FPGA Prototype Verification

To verify a circuit operation of ASIC development, we provide a system to verify designed module circuits and system circuits mapped on FPGAs. This enables even faster processing than RTL simulation by PC, achieving a shorter verification time and long-time process verification.

Advantages

- Enables verification of the designed RTL by running it at near real-time speed.

- Depending on the circuit being verified, verification can be performed in 1/1000th of the time of RTL simulation.

- Software pre-development can be performed before the ASIC is completed.

- Verification in combination with software can be performed.

- Verification for various modules in one environment can be performed.

FPGA Use Cases

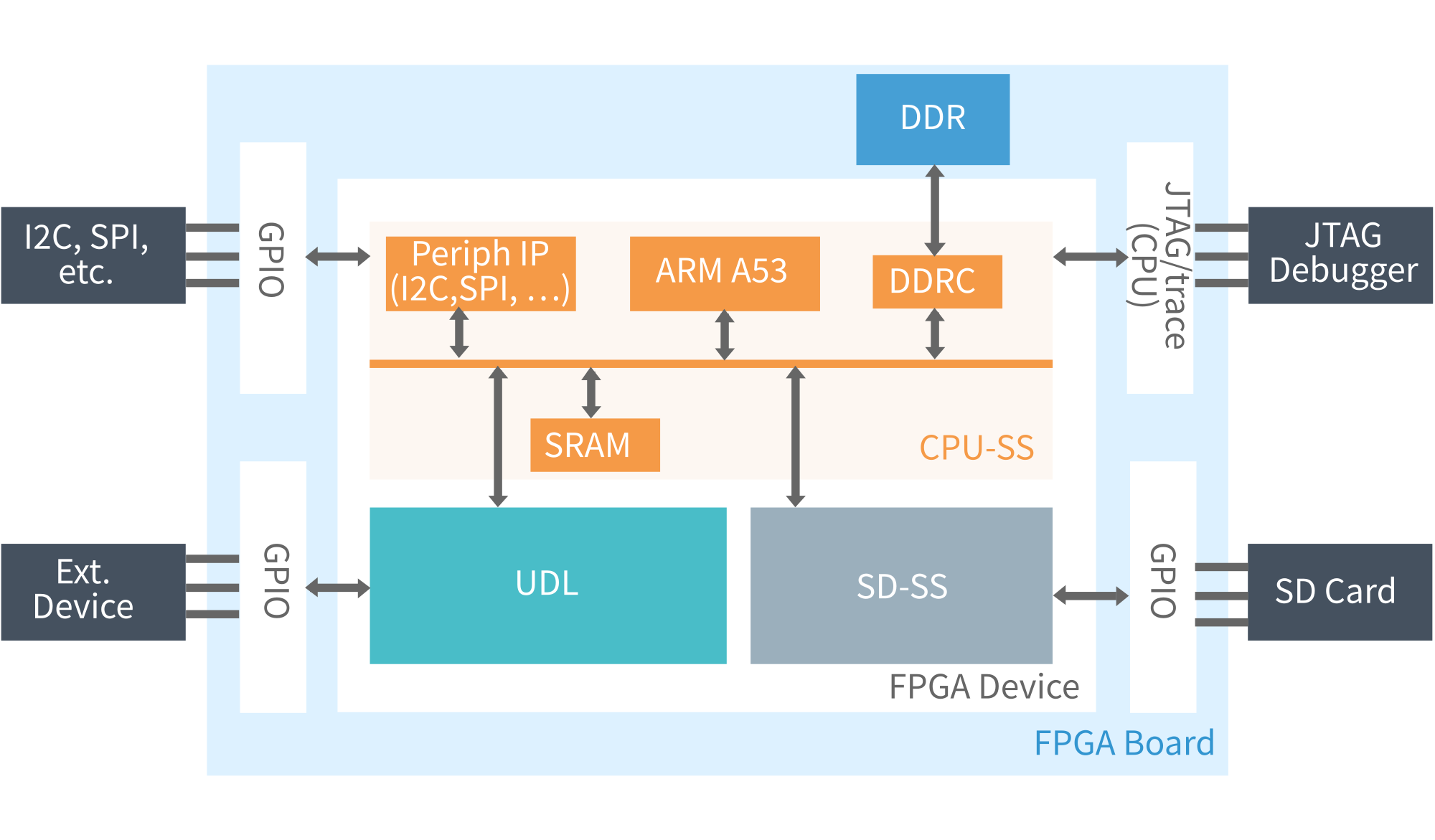

- Implement a CPU subsystem consisting of a processor (ARM, RISC-V, etc.) and peripherals. Sample codes for system initialization and device drivers can be provided.

- Verify operation of embedding UDL in the CPU subsystem.

- Depending on the board configuration, a USB, SD, or eMMC interface can be added on.

- FPGA devices support various grades of other vendors including Xilinx, Intel, and Lattice.

- Supports the encryption of customer UDL and purchased IP, remotely updates bit files, and minimizes TAT from debugging to circuit modification.

Development and Verification Flow Chart

FPGA Verification Example

This example shows the UDL and SD subsystem added to the CPU subsystem based on A53 of ARM. DDR is diverted from the onboard devices.