Development Method and Flow

IP Subsystem

MegaChips develops and provides high-performance and low-power subsystems as a platform that combines the CPU and various IPs, leveraging our extensive experience. With these subsystems, the customers can reduce the time and effort for development as well as focus on their own differentiated technologies.

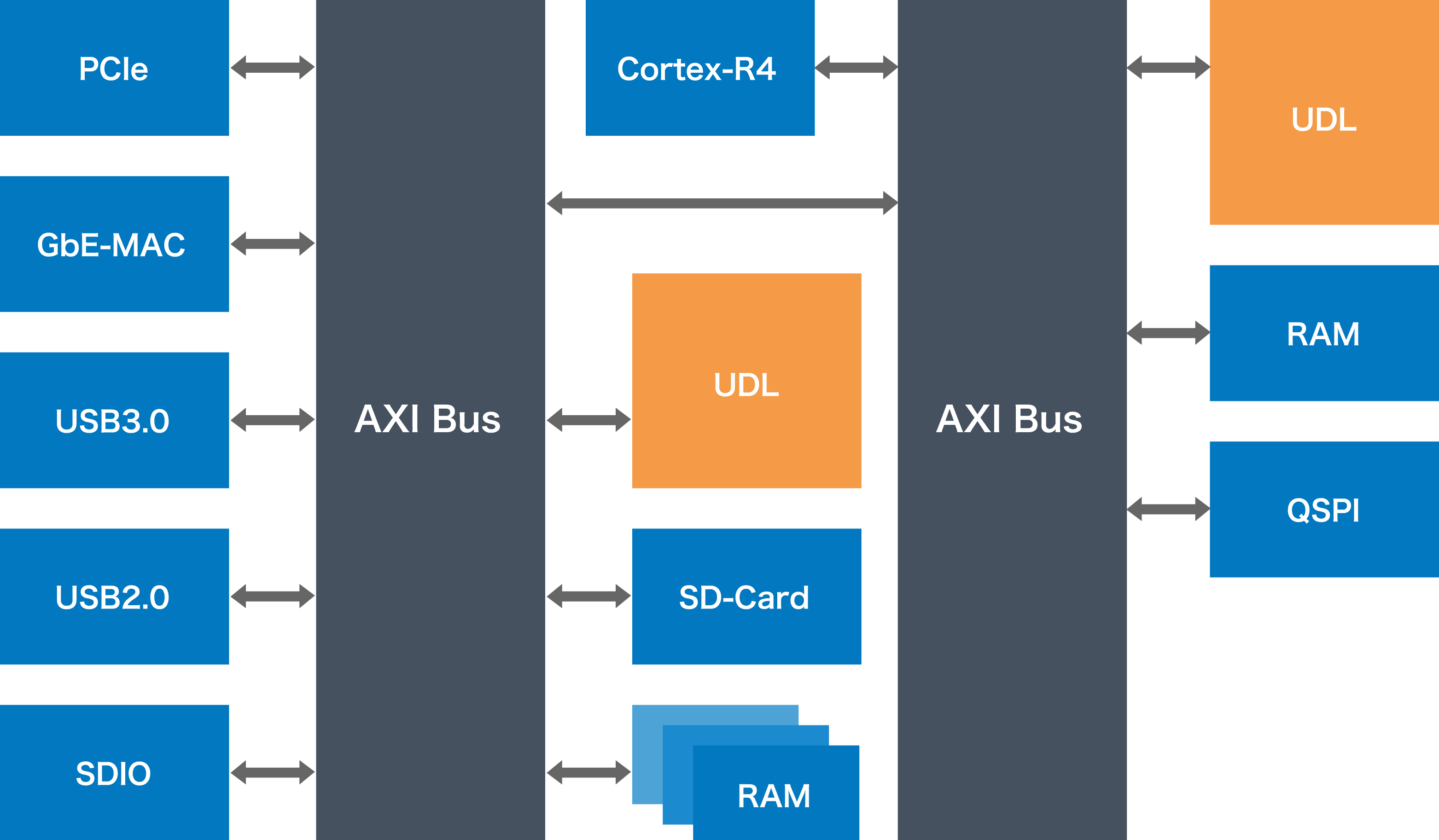

CPU Subsystem

We have over 100 projects utilizing CPU-equipped silicon. We provide optimal CPU subsystems that meet customer needs. In addition, we customize the CPU subsystem based on the request and provide it with a software verification environment.

Function Overview

We work together with our customers to provide customizations for the AXI bus performance and power management in addition to the Arm® processor (Cortex-A family/R family/M family), RISC-V®, DMAC, USB, PCIe, GbE-MAC, SDIO, HDMI, as well as various peripherals and security IPs.

CPU Subsystem Example

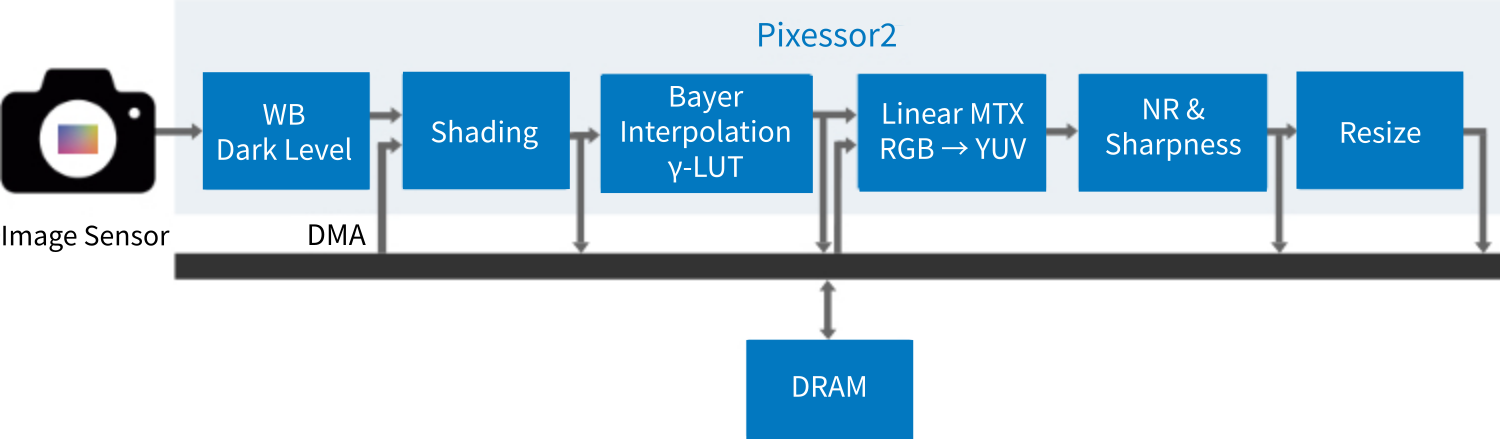

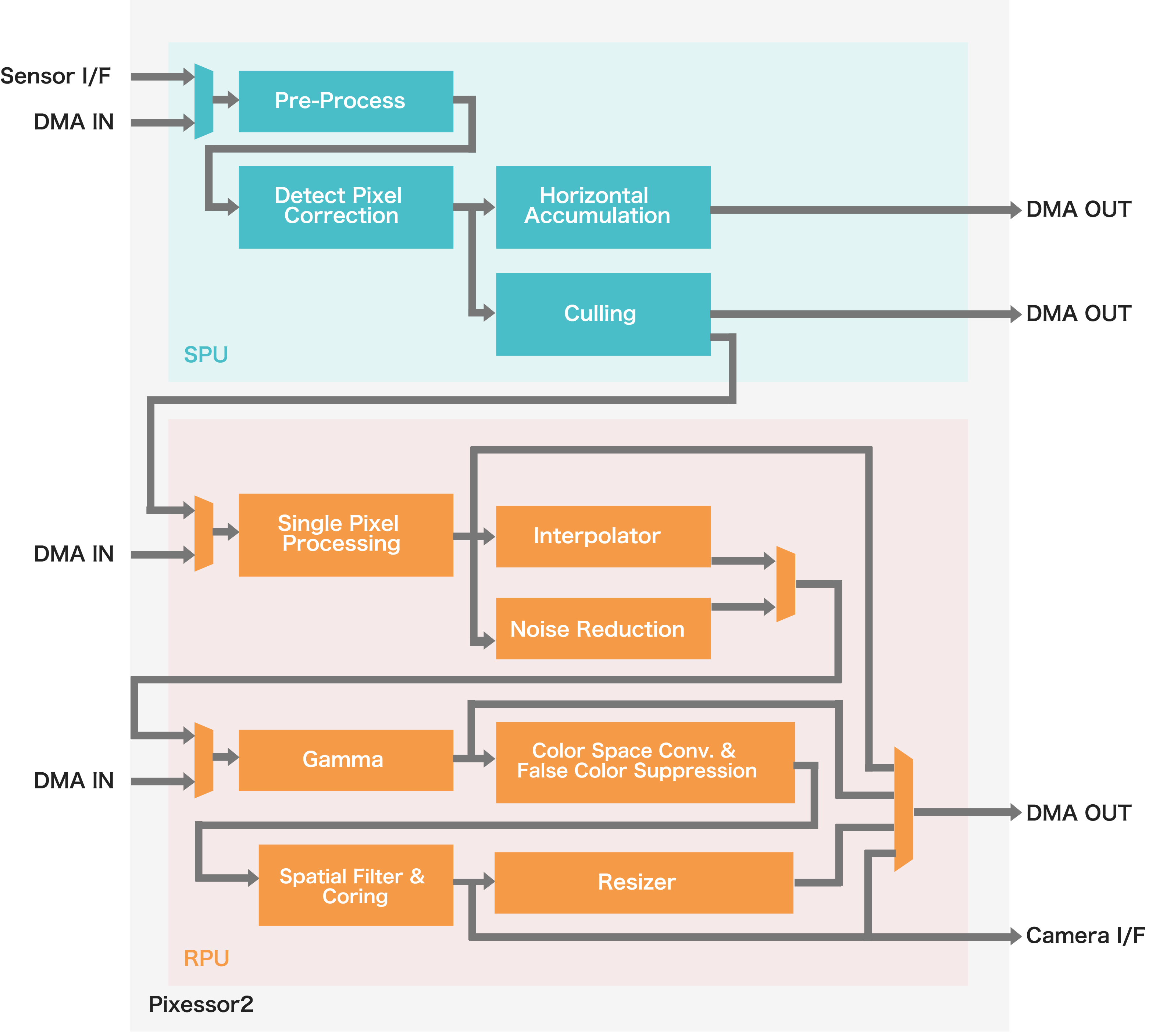

Imaging Signal Processor (ISP) Subsystem

The Pixessor2™ image signal processor (ISP) is a proprietary high-speed processing engine for 2D images and has been adopted in multiple DSLR cameras and smartphones. We customize it upon request and provide it as a high-definition and high-performance subsystem.

Function Overview

Pixessor2™ achieves high performance and high processing using hardware based on pipeline processing, also offering scalability and flexibility like a DSP. In addition, coring and various filter processes are equipped with our proprietary line segment detection algorithm, achieving high definition and noise reduction.

Pixessor2™ Block Diagram

Main Features

- Defect Pixel Correction

- 2D Color Enhancer

- Shading Correction

- Bad Pixel Correction

- Linearization Correction

- Dark Level Correction

- Coring

- Dark Noise Removal

- Affine(Distortion Correction, Fisheye Panorama Correction)

The ISP subsystem consists of the following “Camera Signal Processing Technology (Pixessor-IP)” and “Distortion Correction IP (Affine)”.

1. Camera Signal Processing Technology (Pixessor-IP)

Pixessor-IP processes RAW (Bayer) data from digital cameras at high speed. It reads out image data from memory, corrects distortions, and outputs it back to the memory. This IP is embedded in DSLR cameras and smart devices.

Main Features

- Implements processes necessary for camera image processing (including demosaicing, white balance, and gain processing) in a lot of hardware blocks

- Real-time processing by flexibly combining each processing block

2. Distortion Correction IP (Affine)

Affine is a proprietary distortion image correction IP. It reads out image data from memory, corrects distortions, and outputs it back to the memory.

Function Overview

It corrects barrel and pincushion distortion caused by lens distortion. By changing the parameters, flexible processing combined with trimming, linking, rotating, inverting, enlarging, and reducing is possible.

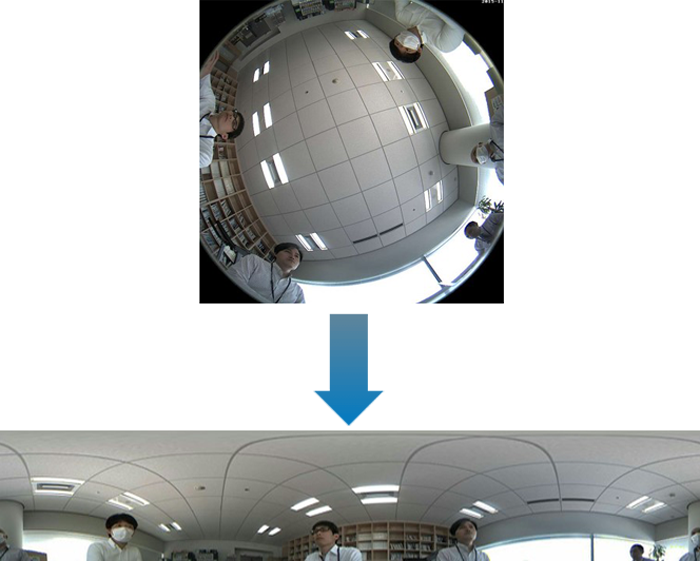

Correction Image (e.g., fisheye panorama correction)

Distortion Correction

Fisheye Panorama Correction

Main Features

- Distortion correction

- Trimming, linking

- Rotating, inverting

- Enlarging and reducing

- Fisheye panorama correction

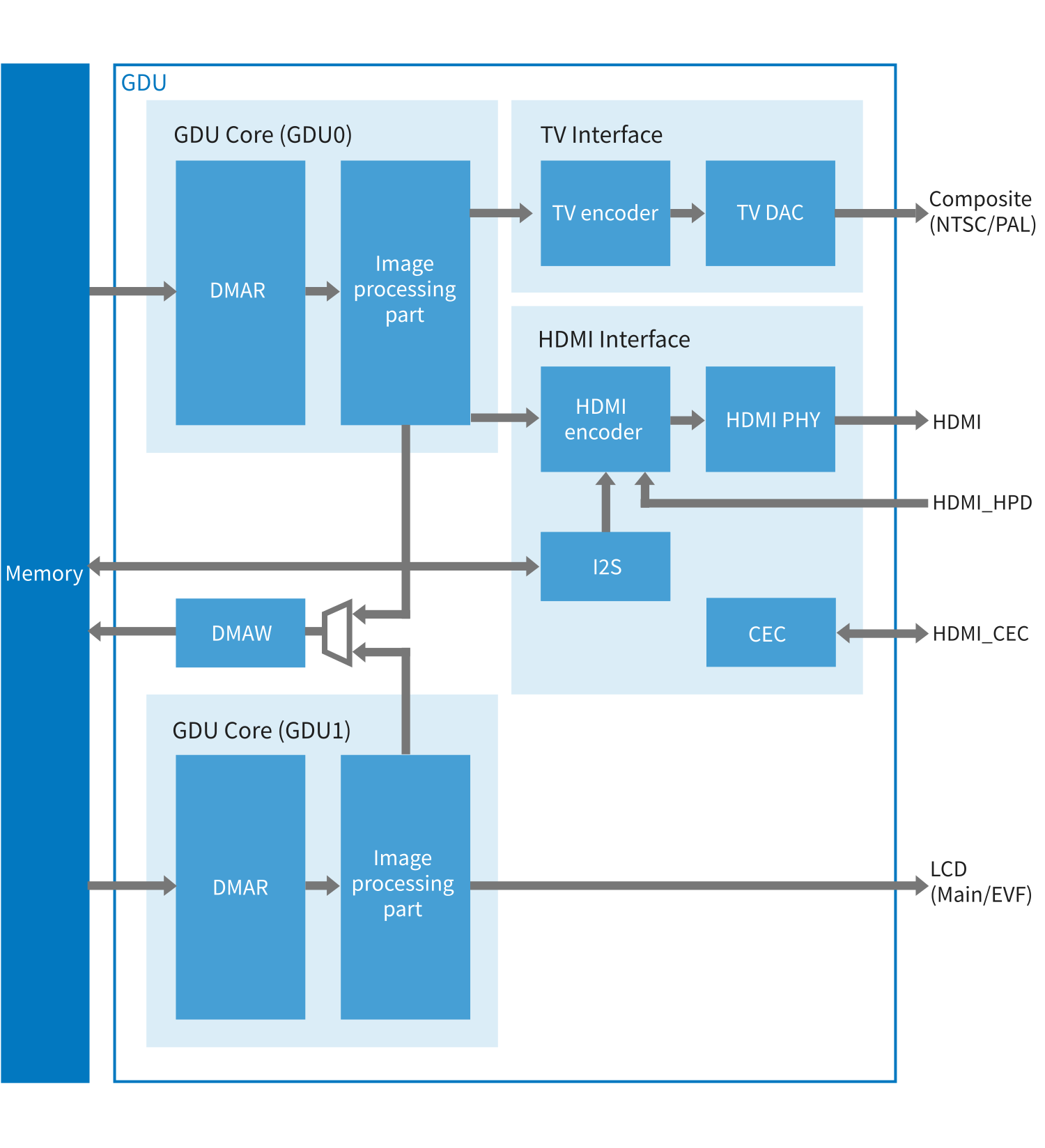

Graphic Display Unit (GPU) Subsystem

GPU is a proprietary image display IP. It reads out the data of multiple images from memory, and outputs it to external devices such as the LCD or HDMI.

Function Overview

This is equipped with general display functions (layering, alpha blending, window, and auto recovery functions). It can generate various synchronizing signals and flexibly support the interface of the required applications. Different types of image corrections are also available.

GDU Block Diagram

Main Features

- Rectangle read-out

- Horizontal/vertical flip

- 180° rotation

- Padding

- Zebra-pattern display

- Blink-pattern display